# Synthesis of Reactive Systems

Jens Regenberg <regenberg@react.cs.uni-sb.de>

Diploma Thesis

Prof. Bernd Finkbeiner Naturwissenschaftlich-Technische Fakultät I Fachrichtung 6.2 – Informatik Universität des Saarlandes, Saarbrücken, 2005

Hiermit erkläre ich an Eides Statt, dass ich die vorliegende Arbeit selbstständig verfasst und keine anderen als die angegebenen Quellen und Hilfsmittel verwendet habe. Saarbrücken, December 4, 2005.

Jens Regenberg

Acknowledgements

I am indebted to many people who have helped me during my studies and in preparing this thesis. I want to thank Bernd Finkbeiner who offered Tobias Maurer and me the topic of our theses. Sven Schewe was a great tutor and patiently answered all questions. Special thanks to Tobias Maurer with whom I developed Rea*Syn* and of course to my parents Uschi and Uwe Regenberg and my fiancée Nina, who supported me througout my whole studies. I love you!

# Contents

| Abstract 1 |                            |                                                   |                    |  |

|------------|----------------------------|---------------------------------------------------|--------------------|--|

| 1          | <b>Intro</b><br>1.1<br>1.2 | oduction History of System Synthesis Our Approach | <b>2</b><br>3<br>3 |  |

| Ι          | The                        | ory                                               | 6                  |  |

| 2          | Preli                      | iminaries                                         | 8                  |  |

|            | 2.1                        | Architectures                                     | 8                  |  |

|            | 2.2                        | Syntax and Semantics of LTL                       | 9                  |  |

|            | 2.3                        | Partition of the Distributed Synthesis Problem    | 11                 |  |

| 3          | Gan                        | ies                                               | 12                 |  |

|            | 3.1                        | Infinite Games                                    | 12                 |  |

|            | 3.2                        | Strategies and Trees                              | 14                 |  |

| 4          | Arcł                       | nitecture Transformations                         | 16                 |  |

|            | 4.1                        | Information Forks                                 | 16                 |  |

|            | 4.2                        | Finding Information Forks                         | 17                 |  |

|            | 4.3                        | Elimination of Idle Processes                     | 19                 |  |

|            | 4.4                        | Quotient Architecture                             | 20                 |  |

|            | 4.5                        | Elimination of Feedback Edges                     | 20                 |  |

|            | 4.6                        | Pipeline Encoding                                 | 22                 |  |

|            | 4.7                        | Game Encoding                                     | 24                 |  |

| 5          | Auto                       | omata                                             | 25                 |  |

|            | 5.1                        | VWAA to Generalized Büchi Automata                | 27                 |  |

|            | 5.2                        | Generalized Büchi Automata to Büchi Automata      | 27                 |  |

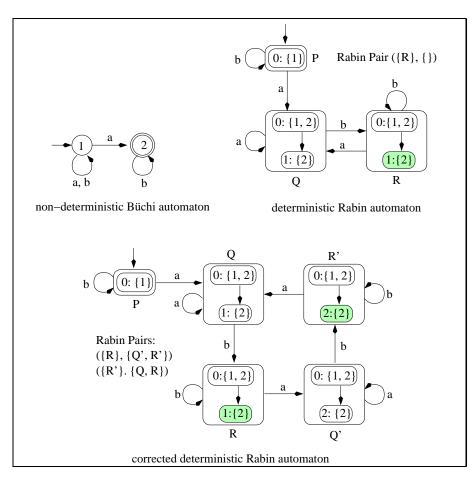

|            | 5.3                        | Determinization of Büchi Automata                 | 28                 |  |

|            | 5.4                        | Rabin Automaton to Parity Automaton               | 31                 |  |

|            | 5.5                        | Parity Automaton to Büchi Automaton               | 32                 |  |

|            | 5.6                        | State Space Reduction of Büchi Automata           | 34                 |  |

| 6         | Spee                                                                                           | cification Transformation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36                                                                                                                                                                                 |

|-----------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 6.1                                                                                            | LTL to Very Weak Alternating Automaton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 36                                                                                                                                                                                 |

|           | 6.2                                                                                            | Games for Automata                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37                                                                                                                                                                                 |

|           |                                                                                                | 6.2.1 Deterministic Parity Automaton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38                                                                                                                                                                                 |

|           |                                                                                                | 6.2.2 Deterministic Büchi Automaton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 38                                                                                                                                                                                 |

| 7         | Win                                                                                            | ning Condition Transformation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39                                                                                                                                                                                 |

|           | 7.1                                                                                            | Non-deterministic Parity Automaton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40                                                                                                                                                                                 |

|           | 7.2                                                                                            | Parity Game                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40                                                                                                                                                                                 |

|           |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                    |

| Π         | Re                                                                                             | $\mathbf{a}Syn$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 42                                                                                                                                                                                 |

| 8         | Use                                                                                            | r Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44                                                                                                                                                                                 |

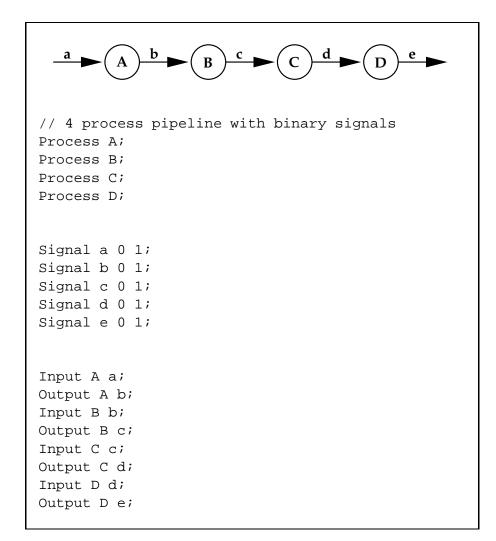

|           | 8.1                                                                                            | Architecture Syntax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44                                                                                                                                                                                 |

|           |                                                                                                | 8.1.1 Process and Signal Declaration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44                                                                                                                                                                                 |

|           |                                                                                                | 8.1.2 Connecting Processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45                                                                                                                                                                                 |

|           | 8.2                                                                                            | Specification Syntax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 47                                                                                                                                                                                 |

|           |                                                                                                | 8.2.1 LTL formula                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47                                                                                                                                                                                 |

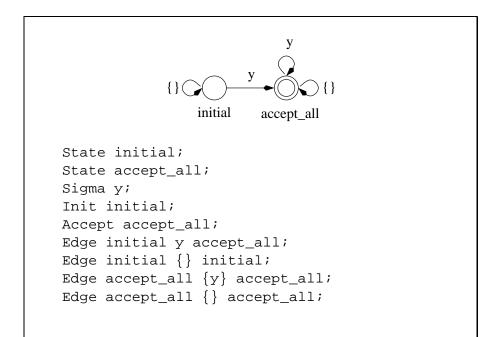

|           |                                                                                                | 8.2.2 Büchi Automata                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48                                                                                                                                                                                 |

|           | 8.3                                                                                            | Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50                                                                                                                                                                                 |

|           | 8.4                                                                                            | Code Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51                                                                                                                                                                                 |

| 9         | Inte                                                                                           | rnal Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54                                                                                                                                                                                 |

|           |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                    |

| 10        | Imp                                                                                            | lementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57                                                                                                                                                                                 |

| 10        | -                                                                                              | lementation Specification Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>57</b><br>57                                                                                                                                                                    |

| 10        | -                                                                                              | Specification Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                    |

| 10        | -                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57                                                                                                                                                                                 |

| 10        | 10.1                                                                                           | Specification Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br>58                                                                                                                                                                           |

| 10        | 10.1<br>10.2                                                                                   | Specification Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br>58<br>58                                                                                                                                                                     |

| 10        | 10.1<br>10.2                                                                                   | Specification Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br>58<br>58<br>59                                                                                                                                                               |

| 10        | 10.1<br>10.2                                                                                   | Specification Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br>58<br>58<br>59<br>60                                                                                                                                                         |

| 10        | 10.1<br>10.2                                                                                   | Specification Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br>58<br>58<br>59<br>60<br>60                                                                                                                                                   |

|           | 10.1<br>10.2<br>10.3                                                                           | Specification Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br>58<br>58<br>59<br>60<br>60<br>63                                                                                                                                             |

|           | 10.1<br>10.2<br>10.3<br><b>Rea</b>                                                             | Specification Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br>58<br>58<br>59<br>60<br>60<br>63<br>64                                                                                                                                       |

|           | 10.1<br>10.2<br>10.3<br><b>Rea</b><br>11.1                                                     | Specification Transformations10.1.1 Fast LTL to Büchi Automata10.1.2 Game Encoding10.1.2 Game EncodingArchitecture TransformationsCode Generation10.3.1 Optimization of the Winning Region10.3.2 Strategy Determinization10.3.3 Generating Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57<br>58<br>59<br>60<br>60<br>63<br>64<br><b>69</b>                                                                                                                                |

|           | 10.1<br>10.2<br>10.3<br><b>Rea</b><br>11.1<br>11.2                                             | Specification Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br>58<br>59<br>60<br>60<br>63<br>64<br><b>69</b>                                                                                                                                |

|           | 10.1<br>10.2<br>10.3<br><b>Rea</b><br>11.1<br>11.2<br>11.3                                     | Specification Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br>58<br>59<br>60<br>60<br>63<br>64<br><b>69</b><br>69<br>71                                                                                                                    |

| 11        | 10.1<br>10.2<br>10.3<br><b>Rea</b><br>11.1<br>11.2<br>11.3<br>11.4                             | Specification Transformations       10.1.1 Fast LTL to Büchi Automata         10.1.2 Game Encoding       10.1.2 Game Encoding         Architecture Transformations       10.1.2 Game Encoding         Architecture Transformations       10.1.2 Game Encoding         Code Generation       10.1.2 Game Encoding         10.3.1 Optimization of the Winning Region       10.3.2 Strategy Determinization         10.3.2 Strategy Determinization       10.3.3 Generating Code         Syn in Numbers       10.3.4 Automata         Optimization of Büchi Automata       10.3.5 Size of Architecture Games         Size of Architecture Games       10.3.5 Simple Alternating Bit Protocol                                                                                                                                                                      | <ul> <li>57</li> <li>58</li> <li>58</li> <li>59</li> <li>60</li> <li>60</li> <li>63</li> <li>64</li> <li>69</li> <li>69</li> <li>71</li> <li>72</li> <li>72</li> </ul>             |

|           | 10.1<br>10.2<br>10.3<br><b>Rea</b><br>11.1<br>11.2<br>11.3<br>11.4                             | Specification Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br>58<br>59<br>60<br>60<br>63<br>64<br><b>69</b><br>71<br>72                                                                                                                    |

| 11<br>III | 10.1<br>10.2<br>10.3<br><b>Rea</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>I D</b>               | Specification Transformations       10.1.1 Fast LTL to Büchi Automata         10.1.2 Game Encoding       10.1.2 Game Encoding         Architecture Transformations       10.1.2 Game Encoding         Architecture Transformations       10.1.2 Game Encoding         Code Generation       10.1.2 Game Encoding         10.3.1 Optimization of the Winning Region       10.3.2 Strategy Determinization         10.3.2 Strategy Determinization       10.3.3 Generating Code         Syn in Numbers       10.3.4 Automata         Optimization of Büchi Automata       10.3.5 Size of Architecture Games         Size of Architecture Games       10.3.5 Simple Alternating Bit Protocol                                                                                                                                                                      | <ul> <li>57</li> <li>58</li> <li>58</li> <li>59</li> <li>60</li> <li>60</li> <li>63</li> <li>64</li> <li>69</li> <li>69</li> <li>71</li> <li>72</li> <li>72</li> </ul>             |

| 11<br>III | 10.1<br>10.2<br>10.3<br><b>Rea</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>I D</b><br><b>Eva</b> | Specification Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>57</li> <li>58</li> <li>58</li> <li>59</li> <li>60</li> <li>60</li> <li>63</li> <li>64</li> <li>69</li> <li>69</li> <li>71</li> <li>72</li> <li>72</li> <li>74</li> </ul> |

| 11<br>III | 10.1<br>10.2<br>10.3<br><b>Rea</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>I D</b><br><b>Eva</b> | Specification Transformations       10.1.1 Fast LTL to Büchi Automata         10.1.2 Game Encoding       10.1.2 Game Encoding         Architecture Transformations       10.1.2 Game Encoding         Architecture Transformations       10.1.2 Game Encoding         Code Generation       10.1.2 Game Encoding         10.3.1 Optimization of the Winning Region       10.3.1 Optimization of the Winning Region         10.3.2 Strategy Determinization       10.3.3 Generating Code         10.3.3 Generating Code       10.3.3 Generating Code         Syn in Numbers       10.3.4 Automata         Optimization of Büchi Automata       10.3.5 Size of Architecture Games         Size of Architecture Games       10.3.5 Simple Alternating Bit Protocol         Simple Alternating Bit Protocol       10.3.4 Game Size Simple Alternating Bit Protocol | 57<br>58<br>58<br>59<br>60<br>60<br>63<br>64<br>69<br>71<br>72<br>72<br>72<br>72<br>74<br>75                                                                                       |

| 11<br>III | 10.1<br>10.2<br>10.3<br><b>Rea</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>I D</b><br><b>Eva</b> | Specification Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br>58<br>58<br>59<br>60<br>60<br>63<br>64<br>69<br>69<br>71<br>72<br>72<br>72<br>74<br>75<br>75                                                                                 |

| 13 Future Directions                        | 77 |

|---------------------------------------------|----|

| 13.1 Further Improvements and Optimizations | 77 |

| 13.1.1 CTL                                  | 77 |

| 13.1.2 Partial Functions                    | 77 |

| 13.1.3 Optimization for Automata            | 78 |

| 13.1.4 Whiteboxes                           | 78 |

| 13.2 Applications                           | 78 |

#### Abstract

Software development generally implies three phases, design, implementation, and verification. As the separation of implementation and verification is timeconsuming and effortful, both phases can be replaced by an automated synthesis development phase. The problem of distributed synthesis is to examine whether for a specification and an architecture there exists an implementation that meets the specification. ReaSyn is a tool, which examines for a given architecture and specification whether the underlying distributed system is realizable and creates an according program. Existing theoretical approaches were implemented: ReaSyn constructs and solves distributed games [MW03] in order to generate an optimized PROMELA program. Finally, ReaSyn is evaluated with respect to experimental results and possible extensions are discussed.

# Chapter 1

# Introduction

Software development is a time-consuming task. Usually it follows three steps. First, all components of the piece of software are designed and their behavior is specified. The design phase is followed by the implementation of the system. Only after the implementation is finished, it is possible to verify the system, i.e., to prove that the implementation satisfies the specified behavior.

An alternative to the effortful tasks of implementation and subsequent verification is to synthesize the implementation. Using a given specification and architecture, synthesis combines implementation and verification in one automated development phase. The resulting program does not require an extensive verification, because due to the synthesis process, the correctness of the program is inherently given. Thus, given an architecture and a specification, synthesis allows to directly create a program, which fulfills the specification. The resulting implementation is defined as a set of finite state programs satisfying the specification. If the given system is not limited to one, but entails several processes, the synthesis is referred to as *distributed synthesis*. Besides automation, synthesis has other advantages. Unrealizable specifications are identified before time is wasted in the implementation process. Additionally, the debugging cycles, which may not even terminate in cases of unrealizable specifications, become obsolete.

The goal of this project was to develop a tool, ReaSyn, which examines whether distributed systems are realizable. Additionally, if they are realizable, a small implementation of the system should be generated. ReaSyn was realized in cooperation with Maurer [Mau05].

So far, research has not provided an implementation of the theoretical aproaches to distributed synthesis. Distributed synthesis is a problem with non-elementary complexity. A second aim of this project was hence to evaluate whether distributed synthesis is possible at all. If so, the goal was to identify its boundary conditions.

## 1.1 History of System Synthesis

Generally, it has been demonstrated that synthesis of reactive systems is possible, but so far, no implementation has been presented. Pnuelli and Rosner [PR90] have shown that the Distributed Synthesis Problem in general is not decidable. This insight was influenced by the work of Peterson and Reif [PR79] who studied multi-player games with incomplete information. But there are classes of architectures, for which the Distributed Synthesis Problem is proven to be decidable. Rosner [Ros92] approached the synthesis of distributed asynchronous systems with LTL (linear temporal logic) specifications. The synthesis problem for a single process architecture was solved for the specification logic CTL<sup>\*</sup> (computational tree logic) [KV97, KV99] as well as for the  $\mu$ -calculus [KV00]. Two-way pipelines and one-way ring architectures with CTL\* specifications are proven to be decidable in [KV01]. Another approach to distributed synthesis was made by Madhusudan and Thiagarajan [MT01, MT02a, ?]. They solved the synthesis problem for LTL in an asynchronous setting. Furthermore, Finkbeiner and Schewe found a criterion [FS05] by which one can efficiently decide whether for a given architecture the distributed synthesis problem is decidable.

There are several approaches to solve the Distributed Synthesis Problem. [PR90] synthesize a program for a single process architecture and subsequently decompose this program into distinct programs for all processes of the architecture. The algorithms of [FS05, KV01] use an automata-based construction. It starts with an automaton equivalent to the specification. In the following, the architecture is incorporated into this automaton. There exists an implementation if and only if the language of the resulting automaton is not empty. A game-theoretic approach is proposed in [MW03]. Here, the specification and the architectures are first encoded into two-player games of player versus environment. In an iterative procedure, the specification game and an architecture game are combined into a new game. The result is a single, solvable two-player game [GTW02]. If and only if there exists a winning strategy for the player, there also exists an implementation that satisfies the specification.

## 1.2 Our Approach

Even though the literature offers the aforementioned theoretical solutions, none of them has been actually implemented. Therefore, ReaSyn was created as a tool to solve instances of the Distributed Synthesis Problem. The problem of distributed synthesis is to examine whether for a specification  $\varphi$  and an architecture  $\mathcal{A}$  there exists an implementation for  $\mathcal{A}$  that satisfies  $\varphi$ .

A Distributed Synthesis Problem is constituted of an architecture and a specification. Architectures model the structure and the internal communication

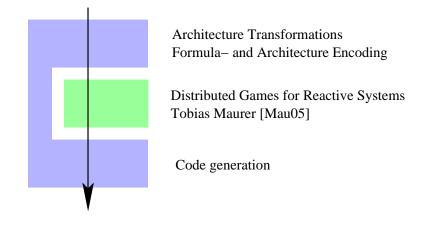

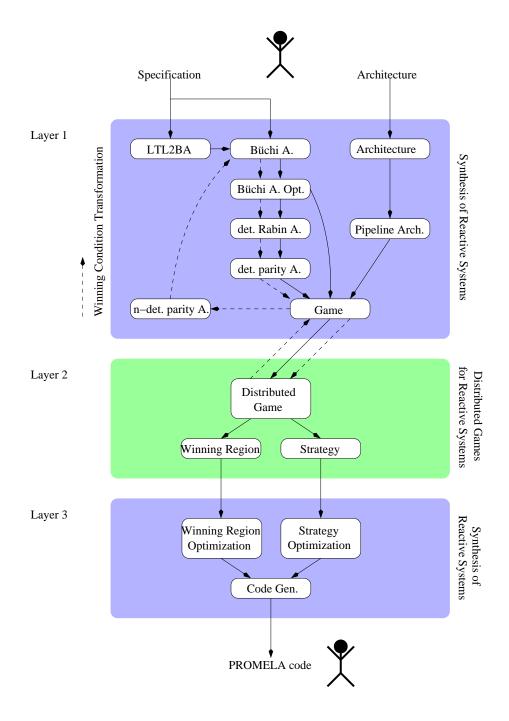

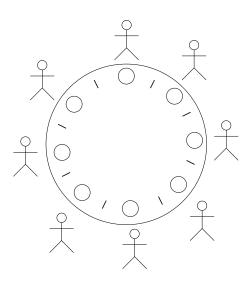

FIGURE 1.1 Interaction between the two theses

of the distributed system, while the specification defines its desired behavior. The efford needed to solve the Distributed Synthesis Problem depends on the sizes of the architecture and the specification. Finkbeiner and Schewe [FS05] introduced the "Information Fork" criterion, which identifies architectures for which the Distributed Synthesis Problem is decidable. For this decidable subclass, Rea*Syn* decides whether the distributed systems are realizable, given a specification in linear temporal logic (LTL).

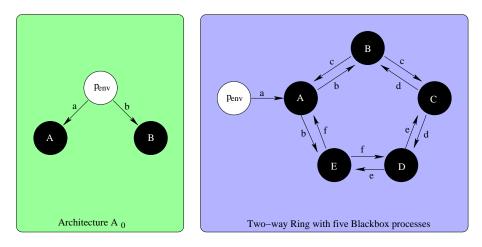

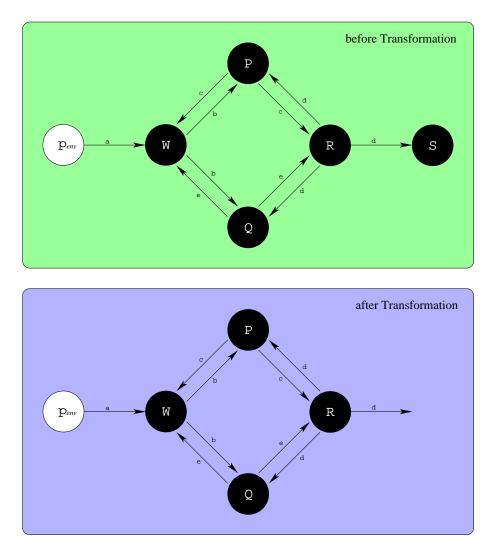

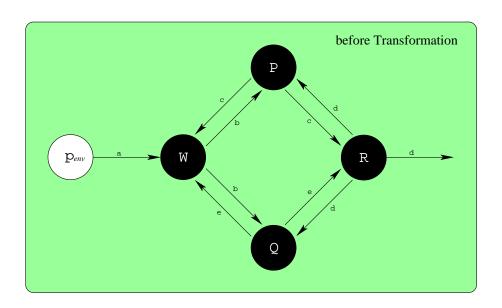

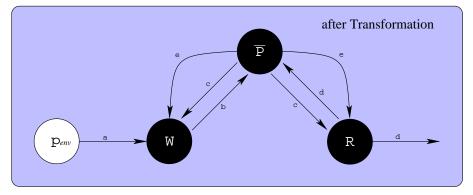

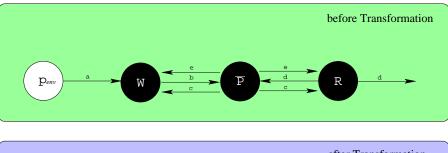

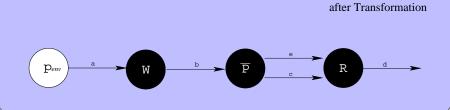

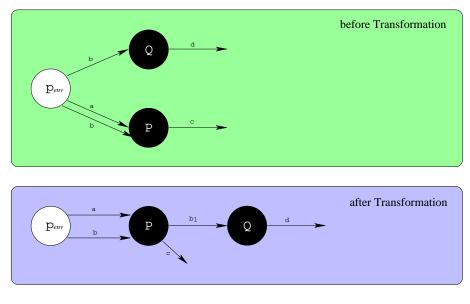

In order to solve such instances of the Distributed Synthesis Problem ReaSyn takes a distributed games approach as proposed by Mohalik and Walukiewicz [MW03]. Due to the restrictions a distributed game imposes on the architectures, the architecture provided by the user is transformed into a pipeline architecture. Therefore, the transformations discussed in [FS05], which transform every architecture without an information fork into a strictly hierarchical acyclic architecture, are used. Finally, the architectures are converted into pipeline architectures. From the solution of the Distributed Synthesis Problem on pipeline architectures a solution for the originally provided architectures is derived.

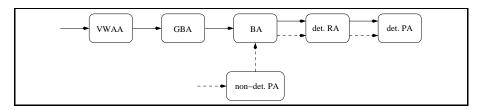

Additionally, a transformation chain is introduced to convert the LTL specification provided by the user into a deterministic automaton. The transformation of the LTL specification uses the tool LTL2BA by Gastin and Oddoux [GO01] to convert the specification into a Büchi automaton. In order to reduce the size of the specification part in the distributed game, the Büchi automaton is optimized before further transformations. Finally, a two-player game simulating the deterministic automaton is used to construct the distributed game. Subsequently, the distributed game is step-wise reduced to a two-player game of Player versus Environment. If the Player wins the game, he has a winning strategy and the distributed system is realizable. The winning strategy is used to create a finite transition system for each process of the original architecture. It is represented as a PROMELA program. ReaSyn was developed in cooperation with Maurer [Mau05]. He focused on the distributed games including the datastructures and algorithms to reduce and solve the distributed games. The present work covers architecture and specification transformations as well as the decomposition and optimization of strategies and the code generation. Additionally, it introduces an automata based transformation of winning conditions. Figure 1.1 gives an overview of ReaSyn's structure. The first part (Chapters 2 - 7) covers the underlying theory of the architecture and specification transformations. Next, ReaSynand its implementation are introduced in detail (Chapters 8 - 10). Finally, the work is evaluated with respect to experimental results and possible extensions are discussed.

# Part I

# Theory

The following chapters formally define the Distributed Synthesis Problem and its components architecture and specification. The architectures describe the structure of the distributed system under consideration. They can be considered as a directed labled graph, where the processes are represented as nodes and the signals, by which the processes communicate, are the edges between the nodes. In every architecture there is a designated process, which simulates the environment in which the distributed system is executed. In fact, in a distributed system every process interacts with a different environment, but as a simplification all these different environment processes are combined. In context of ReaSun the communication via the signals happens without delay. In a single atomic step of the system, all processes of the architecture read input from incoming signals and produce their output. Additionally, ReaSun assumes that the processes of an architecture can be ordered according to their knowledge of the distributed system. Processes, which receive input directly from the environment process are the best informed processes. The less informed processes read their input from the processes with greater knowledge. The specification defines the desired behavior of the distributed system. It is given as an LTL formula. Generally, the behavior of a system is represented as a tree, where different branches denote different behaviors of the system. The different behaviors arouse due to varying input values on the signals under environment control. In order to check whether such a tree satisfies an LTL formula, the LTL formula is tested on every possible path of the tree representing the behavior of the distributed system.

In order to combine both the architecture and the specification into a distributed game [MW03] they have to be converted into two player parity games. If possible, the architecture is first transformed into a pipeline architecture. The resulting pipeline architecture is subsequently encoded into a parity game for each process of the pipeline. One player simulates the process' behavior; the other player chooses the input of the process. The transformation of the specification is more complex. It involves several automata and conversions between them. In the end, the specification is transformed into a deterministic parity automaton, which is encoded into a game simulating the automaton. One player chooses a letter from the automaton's alphabet, the other chooses the transition the automaton would take. In the distributed game, the architecture games are used to generate a behavior pattern of the distributed system and the specification.

Games are introduced in Chapter 3. The transformations used to convert an architecture into a set of two-player games are presented in Chapter 4, while the specification transformations are presented in Chapters 5 and 6. The following chapter covers the formal definition of the Distributed Synthesis Problem and its components.

# Chapter 2

# **Preliminaries**

#### 2.1 Architectures

Architectures structure the way processes communicate with each other. The communication media are called signals. Signals can be written to and read by processes. Interpreting processes as nodes and signals as connecting edges allows to think of an architecture as a directed labled graph.

#### **Definition 1:** Architecture

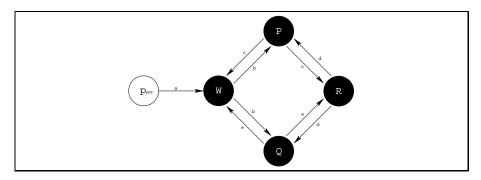

An Architecture is given as a tuple  $\mathcal{A} = (P, S, E_S, p_{env}, I, O)$ where P is the set of processes and  $p_{env} \in P$  is the designated environment process, S is the set of signals (variables).  $I : P \rightarrow 2^S$  is a function that maps a process to the set of its input signals and analogously  $O : P \rightarrow 2^S$  is a function that maps a process to its set of output signals. Furthermore,  $S = \bigcup_{p \in P} O(p)$ ;  $E_S \subseteq P \times S \times P$  is the set of edges labeled with signals. Additionally,  $(p, s, q) \in E_S \Leftrightarrow s \in O(p) \land s \in I(q)$ .

In addition to the definition, the following notation is used: Architecture  $\mathcal{A}$  is called acyclic if  $(P, E_S)$  is acyclic. A signal's domain dom $(s), s \in S$  is the set of values s can hold. A process  $p \in P$  is called idle if  $O(p) = \emptyset$ .  $P^- = \{p \in P \setminus \{p_{env}\} \mid O(p) \neq \emptyset\}$  is the set of non idle processes. In order to avoid inconsistencies, we also assume that the sets O(p) are pairwise disjoint  $(\forall p_1, p_2 \in P.p_1 \neq p_2 \Rightarrow O(p_1) \cap O(p_2) = \emptyset)$ . This means that each signal can only be written to by a single process. However, there is no restriction on how many processes can read a signal. The set  $O(p,q) = \{s \in S \mid (p, s, q) \in E_S\}$  is the set of signals, which label the edges between p and q.  $READ : S \rightarrow 2^P$  returns the set of processes reading the given signal. The corresponding function  $WRITE : S \rightarrow 2^P$  returns the set of processes, which are writing to the specified signal. Note that in our setup WRITE(s) is always a singleton set to avoid inconsistencies. Furthermore, the set  $D(S') = \operatorname{dom}(s_1) \times \cdots \times \operatorname{dom}(s_n)$  is defined to be the cartesian product of signal domains, where  $S' = \{s_1, \ldots, s_n\} \subseteq S$ .

### 2.2 Syntax and Semantics of LTL

LTL formulas are used to describe the execution properties of a system. The set *atom* of atomic propositions contains all properties that can be valid in a given state of the system. Using the boolean operators  $(\lor, \land, \neg)$ , one can express static properties. The temporal operators next (X), until (U), eventually  $(\diamondsuit)$  and henceforth  $(\Box)$  provide the possibility to state dynamic properties.

Definition 2: Syntax of LTL Formulas [GO01]

The set of LTL formulas on the set atom of atomic Propositions is defined by

$$\begin{split} \varphi &::= p \mid \neg \varphi \mid \varphi_1 \lor \varphi_2 \mid \varphi_1 \land \varphi_2 \\ \mid \mathbf{X} \varphi \mid \diamond \varphi \mid \Box \varphi \mid \Box \varphi \mid \varphi_1 \: \mathbf{U} \: \varphi_2 \end{split}$$

```

where p \in atom.

```

An LTL formula can be interpreted regarding different types of systems. Usually, it is interpreted with respect to a linear structure but it can be interpreted with regard to a tree-like structure as well. In a tree, every path resembles an execution behavior of the system. The LTL formula is interpreted over every possible path in the tree. A linear model can be seen as a unary tree. In case of a linear system one speaks of word semantics of LTL. The semantics, which interpret LTL formulas over arbitrary trees, are called tree semantics of LTL.

**Definition 3**:  $\Sigma$ -labeled  $\Upsilon$ -tree

A (full) tree is given as the set  $\Upsilon^*$  of all finite words over a set of directions  $\Upsilon$ . Every non-empty node  $x \cdot v, x \in \Upsilon^*, v \in \Upsilon$ , has the direction  $\operatorname{dir}(x \cdot v) = v$  and the empty word  $\epsilon$  has a designated root direction  $\operatorname{dir}(\epsilon) = v_0 \in \Upsilon$ . Given the finite sets  $\Sigma$  and  $\Upsilon$ , the  $\Sigma$ -labeled  $\Upsilon$ -tree is a pair  $\langle \Upsilon^*, l \rangle$ , where  $l : \Upsilon^* \to \Sigma$  is a labeling function, which maps a node from  $\Upsilon^*$  to a letter of  $\Sigma$ .

#### Definition 4: Run of a System

A run  $\sigma = \sigma_1 \sigma_2 \cdots \in \Sigma^{\omega}$  of a system is a infinite sequence of system states. This sequence resembles a single execution of

the system. Each  $\sigma_i$  contains the valid atomic propositions of the system state.

The word semantics of LTL define whether or not a run  $\sigma$  of a given system satisfies a given formula  $\varphi$ . The semantics depend on the atomic propositions that are valid in the states of  $\sigma$ .

**Definition 5**: Word Semantics of LTL Formulas [GO01]

Let  $\sigma = \sigma_0 \sigma_1 \dots$  be a word in  $\Sigma^{\omega}$  with  $\Sigma = 2^{atom}$  and  $\varphi$  an LTL formula. *atom* is the set of atomic propositions. The relation  $\sigma \models \varphi$  ( $\sigma$  models  $\varphi$ ) is defined as follows:

$\begin{array}{l} -\sigma \models p \text{ iff } p \in \sigma_0, \\ -\sigma \models \neg \varphi \text{ iff } \sigma \not\models \varphi, \\ -\sigma \models \varphi_1 \lor \varphi_2 \text{ iff } \sigma \models \varphi_1 \text{ or } \sigma \models \varphi_2, \\ -\sigma \models x\varphi \text{ iff } \sigma_1 \sigma_2 ... \models \varphi, \\ -\sigma \models \varphi_1 \lor \varphi_2 \text{ iff } \exists k \ge 0.\sigma_k \sigma_{k+1} ... \models \varphi_2 \text{ and } \forall 0 \le i < k.\sigma_i \sigma_{i+1} ... \models \varphi_1. \end{array}$

The additional operators are derived from the basic ones. They are defined by:

- true  $\stackrel{def}{=} p \lor \neg p$

- false  $\stackrel{def}{=} \neg$  true

- $\varphi_1 \wedge \varphi_2 \stackrel{def}{=} \neg (\neg \varphi_1 \lor \neg \varphi_2)$

- $\bullet \ \Diamond \varphi \stackrel{def}{=} \texttt{true U} \varphi$

- $\Box \varphi \stackrel{def}{=} \neg \diamondsuit (\neg \varphi)$

The size of an LTL formula  $\varphi$  is defined as the number of subformulas of  $\varphi$ .

Definition 6: Tree Semantics of LTL Formulas

Let  $\pi = v_1 v_2 \cdots \in \Upsilon^{\omega}, v_i \in \Upsilon^{\star}$  be a path through the  $\Sigma$ -labeled  $\Upsilon$ -tree  $\langle \Upsilon^{\star}, l \rangle$ . The relation  $\models$  is defined by:

$$\langle \Upsilon^{\star}, l \rangle \models \varphi \stackrel{\text{def.}}{\longleftrightarrow} \forall v_1 v_2 \cdots \in \Upsilon^{\omega}. l(v_1) l(v_2) \cdots \models \varphi.$$

## 2.3 Partition of the Distributed Synthesis Problem

Given the above mentioned definitions, one can formally define the Distributed Synthesis Problem:

Definition 7: Distributed Synthesis Problem

For a given architecture  $\mathcal{A}$  and an LTL formula  $\varphi$ , the Distributed Synthesis Problem  $(\mathcal{A}, \varphi)$  is the problem to decide, whether there exists an implementation for  $\mathcal{A}$ , which satisfies  $\varphi$ . Additionally, if there exists such an implementation, the problem extends to finding one of them.

ReaSyn addresses the Distributed Synthesis Problem in three parts:

- 1. Part one, covered in this thesis, handles the transformations needed to convert the specification and the architecture into games. Furthermore, it provides functionality to convert the "all-path parity" condition (cf. Chapter 7) into a parity condition.

- 2. The second part, covered in [Mau05], is concerned with solving a distributed game [MW03].

- 3. Finally, the third part covers the optimization and generation of PROMELA code for the distributed system. It is also covered in this thesis.

A solution to an instance of the Distributed Synthesis Problem is a tree, which satisfies the specification and represents an implementation of the architecture processes. The external input values of the system span this tree; every path starting at the root constitutes a run of the system. Part two creates these trees by combining the architecture games and the specification game. These games are constructed by the first part. The specification game is used to check whether every path in the tree fulfills the specification, while the architecture games create the branches of the tree. Finally, the third part chooses a tree, which solves the given instance of the Distributed Synthesis Problem and generates a PROMELA program induced by the tree.

In order to formalize the interaction of these parts with each other and the user, there are two interfaces. The parts of ReaSyn covered by this thesis interact with two parties, namely, the user and the part described in [Mau05]. The interface controlling the interaction with the user is covered in Chapter 8, while Chapter 9 describes the interface between parts one and two and parts two and three.

# Chapter 3

# Games

This chapter gives a short introduction to infinite two-player games on directed graphs. One player is called Player, the other is called Environment.

### 3.1 Infinite Games

A game consists of an arena and a winning condition.

Definition 8: Arenas [GTW02]

An arena is a triple  $\mathfrak{A} = (V_{player}, V_{env}, E)$ , where  $V_{player}$  is a finite set of nodes belonging to the Player.  $V_{env}$  is the finite set of Environment nodes. The set of all nodes is denoted by  $V = V_{player} \stackrel{.}{\cup} V_{env}$ .  $E \subseteq V \times V$  is the transition relation.

In addition, let  $vE = \{v' \in V \mid (v, v') \in E\}$  be the set of successors of v. For a player  $\sigma \in \{Player, Environment\}, \bar{\sigma}$  determines the remaining player. A bipartite game is a game where Player and Environment nodes alternate on every path through (V, E) ( $\forall v \in V_{\sigma}.vE \subseteq V_{\bar{\sigma}}$ ).

One play of a game can be visualised as follows. A token is placed on an initial node  $v_0$ . If  $v_0$  is a Player node, then the Player moves the token from  $v_0$  to a successor node  $v' \in v_0 E$ . Analogously, if  $v_0$  is an Environment node, the environment moves the token to a successor. Formally, if  $v \in V$  is a  $\sigma \in \{Player, Environment\}$  node then  $\sigma$  chooses one successor  $v' \in vE$ . This procedure is carried out until the token reaches a dead end, i.e., a node v with  $vE = \emptyset$ .

#### **Definition 9**: Play [GTW02]

A play in the Arena  $\mathfrak{A}$  is defined either as

- an infinite path  $\pi = v_0 v_1 v_2 \cdots \in V^{\omega}$  (infinite play)

- or a finite path  $\pi = v_0 v_1 v_2 \dots v_n \in V^+$  (finite play)

with  $\forall i \in \mathbb{N}.v_{i+1} \in v_i E$  in case of an infinite play or  $v_n E = \emptyset \land \forall 0 \leq i < n.v_{i+1} \in v_i E$  in case of a finite play. For an infinite play  $\pi$  the infinity set  $\text{Inf}(\pi)$  is defined to be the set of nodes that occur infinitly often in  $\pi$

Winning conditions for games are the same as the winning conditions for automata. Although there are many more, in the case of ReaSyn, Büchi-, Rabin-, parity, and "all-path" parity winning conditions, as defined below, are applicable. The other mentionend winning conditions appear in the context of LTL2BA [GO01] and will be discussed below. In analogy to the winning conditions for automata, parity winning conditions rely on a coloring function to categorize the existing nodes: let  $\chi : V \to C$  be a coloring function that maps a node to a color. The coloring of a play  $\chi(\pi)$  is defined as  $\chi(v_0)\chi(v_1)\ldots$ .

#### Definition 10: Winning Condition

Let ACC be an arbitrary winning condition. By W(ACC) we denote the set of all infinite plays  $\pi$ , such that  $\pi$  is accepted by ACC. We define the following winning conditions [GTW02]:

- Büchi condition ACC = F ⊆ V: π ∈ W(ACC) if and only if Inf(π) ∩ F ≠ Ø

- co-Büchi condition ACC ⊆ V: π ∈ W(ACC) if and only if Inf(π) ∩ ACC = Ø

- Rabin condition  $ACC = \{(G_0, R_0), (G_1, R_1), \dots, (G_n, R_n)\}$ :  $\pi \in W(ACC)$  if and only if  $\exists 0 \leq k \leq n$  such that  $Inf(\pi) \cap E_k = \emptyset \land Inf(\pi) \cap F_k \neq \emptyset$ .

- minimal parity condition (χ : V → N): π ∈ W(ACC) ⇔ min(Inf(χ(π))) is even.

- generalized Büchi [GO01]: ACC = T ⊆ V × Σ × V. π ∈ W(ACC) ⇔ ∃v<sup>σ</sup>v' ∈ T that appears infinitly often in π. In other words, some transitions from T are taken infinitly often.

In anology to minimal parity conditions there also is a maximal parity condition. There, the maximal parity occuring infinitly often has to be even. During the reduction of the distributed game another winning condition appears,

which is called an "all-path parity" condition. It is introduced in Chapter 7 as some additional definitions are needed.

Finally, a game can be defined:

#### Definition 11: Game [GTW02]

Let  $\mathfrak{A}$  be an arena as above and  $Win \subseteq V^{\omega}$ . The pair

$$\mathcal{G} = (\mathfrak{A}, Win)$$

is called a game. A Tuple  $(\mathcal{G}, v_0)$  is called an initialized game, if every play  $\pi$  begins with  $v_0$ . The Player is declared the winner of a play, if and only if

- $\pi = v_0 v_1 \dots v_n$  is a finite play and  $v_n$  is an Environment node with  $v_n E = \emptyset$  or

- $\pi = v_0 v_1 \dots$  is an infinite play and  $\pi \in Win$ .

The Environment wins  $\pi$ , if the Player does not win  $\pi$ . If the Player wins an initialized game, he is called winner of the game.

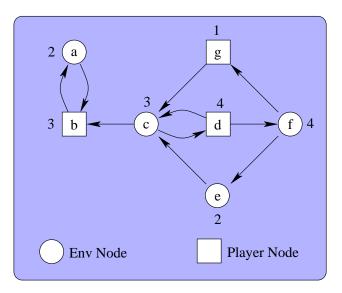

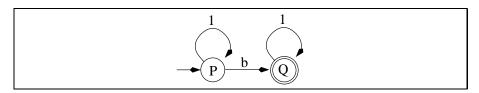

### 3.2 Strategies and Trees

Having defined the possible winning conditions, one needs to examine, whether a player (Player or Environment) can win the game from a given node, regardless of how the other moves. This possibility is given if a player has a strategy leading him through the game in a way that he will win it. Consider the game in Figure 3.1 under the assumption of a min parity winning condition. From node b, Player can only move to node a. The Environment can only move the token back to b. In this cycle the Player wins with the strategy "If I'm in b then I'll move the token to node a". If the game starts in a different node, the Environment will win every play with the strategy: "Whenever the token is in node c, I'll move it to node d and if it is in node f, I'll move it towards node g". If the Environment moves the token from c to b instead of d, it will loose the play because then the Player "can" always stay in  $\{a, b\}$ . Furthermore, if the Environment moves the token from f to e instead of g, Player wins the min parity game. Formally, a strategy is:

#### Definition 12: Strategy [GTW02]

A strategy for player  $\sigma \in \{Player, Environment\}$  is function  $f_{\sigma}: V^*V_{\sigma} \to V$ , which determines a successor for player  $\sigma$  respecting the history of already visited nodes.

In the strategy, the choice of a successor may depend on the already visited nodes. If the strategy for a player  $\sigma$  does not depend on the history of visited nodes, the strategy is called a memoryless strategy.

Definition 13: Memoryless Strategy [GTW02]

A memoryless strategy for player  $\sigma$  is a function  $f_{\sigma}: V_{\sigma} \to V$ , where  $\forall v \in V_{\sigma}: f_{\sigma}(v) \in vE$ . The choice of the successor depends only on the current node. In bipartite games one can even write:  $f_{\sigma}: V_{\sigma} \to V_{\bar{\sigma}}$ .